ESKİŞEHİR TECHNICAL UNIVERSITY

## DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

EEM 334 - Digital Systems II

# <u>LAB 4 – COMBINATIONAL LOGIC CIRCUIT –</u> <u>ALU DESIGN</u>

### **1. PURPOSE**

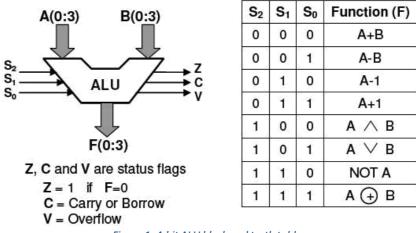

After implementing 4-bit adder on Nexys4 board in previous laboratory, now you are responsible for making an ALU circuit whose block diagram and truth table are given below. Your ALU design must take two 4-bit operands and it must perform Addition, Subtraction, Increment, Decrement, AND, OR, XOR and NOT operations.

#### 2. BACKGROUND

An Arithmetic and Logic Unit (ALU) is a combinational circuit that performs logical and arithmetic operations on a pair of n-bit operands (in our case, A[3:0] and B[3:0]). Unless otherwise stated, you can assume that the inputs A and B are signed, two's complement numbers when they are presented to the input of the ALU. The operations performed by an ALU are controlled by a set of operation-select inputs. In this lab you will design an 4-bit ALU with 3 operation-select inputs, S[2:0]. Logical operations take place on the bits that comprise a value (known as bitwise operations), while arithmetic operations treat inputs and outputs as two's complement integers.

The block diagram and the truth table for the ALU are shown below. You must write the VHDL code for this simple 4-bit ALU according to the following functionality.

#### **3. PROCEDURE**

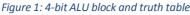

In this lab, you will design 8 modules individually (one of them 4-bit full adder is already designed). Each operation must be designed on different VHDL modules and they can be used on "ALU\_top" module which is written on following pages.

Your module names must be like as shown below:

- 1. four\_bit\_adder.VHD

- 2. four\_bit\_subtract.VHD

- 3. four bit and.VHD

- 4. four\_bit\_or.VHD

- 5. four\_bit\_xor.VHD

- 6. increment.VHD

- 7. decrement.VHD

- 8. NotA.VHD

In addition, you should complete "ALU\_top" module, which is given in the next page to combine your eight components.

Figure 2 ALU\_top module

The lab assistants will allow you to enter into the lab session ONLY IF you bring a pre-lab report that shows you designed each of 8 modules, tested them individually by using Xilinx ISE simulator, and verified each of them to be correct.

To summarize your jobs;

1. Design each of 8 modules and test them individually by using Xilinx ISE simulator.

2. Instantiate all components in ALU\_top.

3. Choose the proper result for "final\_out" with a multiplexer according to "op\_sel" select signal.

4. Create a UCF file and connect your inputs to switches, and flags to LEDs and 7-segment outputs to 7-segment displays on the board.

5. Show your design burned into FPGA to the lab assistants.

You can also make your own complete design without using "ALU\_top" as a template. This template is to help you while you are designing this simple ALU.

*Note That:* You must be ready to implement the task which will be given to you during your lab sessions.

#### ALU\_top

libraryIEEE; use IEEE.STD\_LOGIC\_1164.ALL; entity ALU\_top is Port(clk:inSTD LOGIC; in1 : in STD\_LOGIC\_VECTOR (3 downto 0); in2 : in STD\_LOGIC\_VECTOR (3 downto 0); op\_sel: in STD\_LOGIC\_VECTOR (2 downto 0); flag\_out : out STD\_LOGIC\_VECTOR (2 downto 0); seg\_out:out STD\_LOGIC\_VECTOR(7 downto 0); seg\_sel:out STD\_LOGIC\_VECTOR(7 downto 0)); endALU\_top; architecture Behavioral of ALU\_top is component four\_bit\_adder Port ( in1 : in STD\_LOGIC\_VECTOR (3 downto 0); in2: in STD\_LOGIC\_VECTOR (3 downto 0); sout : out STD\_LOGIC\_VECTOR (3 downto 0); cout:outSTD\_LOGIC); endcomponent; component four\_bit\_subtract Port( a1:in STD\_LOGIC\_VECTOR(3 downto 0); a2: in STD\_LOGIC\_VECTOR (3 downto 0); out1:outSTD\_LOGIC\_VECTOR(3 downto 0)); endcomponent; componentdecrement Port(a1:inSTD LOGIC VECTOR(3 downto 0); out1:outSTD\_LOGIC\_VECTOR(3 downto 0)); endcomponent; componentincrement Port( a1:inSTD\_LOGIC\_VECTOR(3 downto 0); carry:outSTD\_LOGIC; out1:outSTD\_LOGIC\_VECTOR(3downto0)); endcomponent; componentfour\_bit\_and Port ( a1 : in STD\_LOGIC\_VECTOR (3 downto 0); a2: in STD\_LOGIC\_VECTOR (3 downto 0); out1:outSTD\_LOGIC\_VECTOR(3 downto 0)); endcomponent; componentfour\_bit\_or Port( a1 : in STD\_LOGIC\_VECTOR (3 downto 0); a2: in STD\_LOGIC\_VECTOR (3 downto 0); out1:outSTD\_LOGIC\_VECTOR(3 downto 0)); endcomponent; componentNotA Port ( a1 : in STD\_LOGIC\_VECTOR (3 downto 0); out1:outSTD\_LOGIC\_VECTOR(3 downto 0)); endcomponent;

- --Firstoperand

- --Secondoperand

- --Operationsellect

- -- You should connect them to leds to see changes

-- Component declerations

componentfour\_bit\_xor Port( a1 : in STD\_LOGIC\_VECTOR (3 downto 0); a2: in STD\_LOGIC\_VECTOR (3 downto 0); out1:outSTD\_LOGIC\_VECTOR(3downto0)); endcomponent; component seven\_four Port ( in1 : in STD\_LOGIC\_VECTOR (3 downto 0); in2 : in STD\_LOGIC\_VECTOR (3 downto 0); in3 : in STD\_LOGIC\_VECTOR (3 downto 0); in4 : in STD\_LOGIC\_VECTOR (3 downto 0); clk: in STD\_LOGIC; dp:outSTD\_LOGIC; sel : out STD\_LOGIC\_VECTOR (3 downto 0); segment : out STD\_LOGIC\_VECTOR (6 downto 0)); end component; --Signal declarations before begin block of architecture signal add out, sub out, and out, or out: STD LOGIC VECTOR(3downto0); signal xor\_out, inc\_out, dec\_out, not\_out, final\_out, carry\_show: STD\_LOGIC\_VECTOR(3 downto 0); signaladd\_carry, inc\_carry: STD\_LOGIC; signal Z, V, C : STD\_LOGIC; -- Flag bits signal dp: STD\_LOGIC; signal sel\_out\_7 : STD\_LOGIC\_VECTOR(6 downto 0); signal seg\_sel\_4: STD\_LOGIC\_VECTOR(3 downto 0); signal temp1, temp3 : STD\_LOGIC; signal temp2: STD LOGIC VECTOR(4 downto 0); begin carry\_show<= "000" & C; --To showcarry bit on seven segment (concatenate) A0: four bit adder port map(); -- You should complete the component port maps -- You should also design these modules A1 : four\_bit\_subtract port map(); A2: four\_bit\_and port map(); A3: four\_bit\_or port map(); A4: four bit xor port map(); A5: increment port map(); A6: decrement port map(); A7: NotA port map(); A8 : seven\_four port map (final\_out, carry\_show, "0000", "0000", clk, dp, seg\_sel\_4, seg\_out\_7); -- Seven segment related part  $seg_out \le (seg_out_7 \& dp);$ seg\_sel <= "1111" & seg\_sel\_4; -- Finding the flag\_out output temp1 <= '1' when in2>in1 else **'0'**: temp3  $\leq$  '1' when in1 = "0000" else **'**0':  $V \le \text{temp1}$  when  $\text{op\_sel} = "001"$  else temp3 when  $op_sel = "010"$  else **'**0': C <= add\_carry when op\_sel = "000" else inc\_carry when op\_sel = "011" else **'**0'; temp2 <= final\_out & C;</pre>  $Z \le 1'$  when temp2 = "00000" else **'**0': flag\_out <= Z & C & V; -- concatenation flags. --Your 4-bit 8x1 multiplexer code will be here - end Behavioral: